赛扬352颗颗超5GHz 测试成绩首度曝光

5月28日,Intel正式发布了采用Cedar Mill核心,65nm工艺,512KB L2缓存的赛扬D处理器。发布初期只限于较高端的型号,包括Celeron D 352 (3.2GHz/512KB L2/533MHz FSB)和Celeron D 356 (3.33GHz/512KB L2/533MHz FSB)两款,预计每千颗定价分别为79美元及89美元。早先,Celeron D 356已经在日本零售市场开卖,而最近更低端的Celeron D 352在台湾地区已经现身,据网友测试发现,该处理器和356一样具有惊人的超频能力。

首先,我们为您介绍一下新Celeron D的核心Cedar Mill(具体可参看《AMD终于落后了!65nm新核心P4全面测试》一文。Cedar Mill作为新一代P4核心,实际上并不是一种新的架构,他完全沿用了Prescott核心的设计,所以性能上并没有提升。不过由于采用了先进的65nm制造工艺,使得发热量大幅下降,2MB L2缓存也让其性能备受期待。下面我们来看看Cedar Mill核心具备哪些新技术。

● 继续使用“应变硅”技术

在Cedar Mill当中Intel继续使用其“应变硅”技术来控制高频工作下的漏电流,而不是SOI。应变硅的技术原理是将在MOS管的栅极下沟道处的硅原子的间距加大,减小电子通行所受到的阻碍,也就是相当于减小了电阻,当MOS管打开的时候电流就会更顺利地沿着拉伸方向在源极和漏极之间流动,这样一来半导体器件发热量和能耗都会降低,而运行速度则得以提升。

● 晶体管“深度睡眠”技术

另外,Cedar Mill和Presler(65nm双核)核心都能够自动关闭未使用的晶体管(包括部分缓存区域和其他功能模块),或者说是使这部分晶体管处于深度睡眠状态,而Intel称唤醒这部分晶体管所需时间非常短不会造成性能上的延迟。

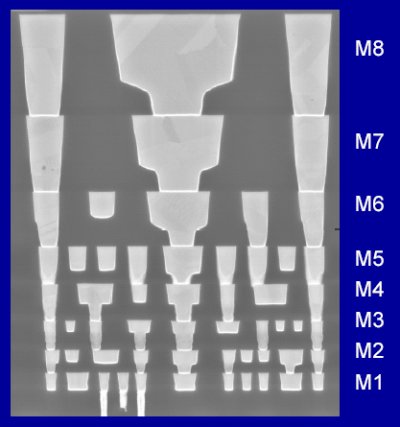

● 65nm工艺8层铜互连技术攻克

从处理器外观上看不出来P4 Cedar Mill和P4 Prescott有什么区别

从处理器外观上看不出来P4 Cedar Mill和P4 Prescott有什么区别

● TDP(设计功耗)降低:

相比早先的Prescott核心,Cedar Mill(3.0到3.6GHz)的设计功耗从95瓦下降到了86瓦,而通过我们的实际测试,在满负荷情况下Cedar Mill的功耗比Prescott(同为2MB二级缓存)下降了20%,由此以来Intel在处理器“每瓦特性能”对比中与AMD差距进一步缩小。

采用Cedar Mill的新Celeron,具备了P4级处理器1/4容量的L2缓存,也就是512KB,这对Celeron系列来说可以说是个相当大的突破。测试中显示,P4处理器缓存由1MB升级到2MB,性能提升并不是很大,这显然是受核心架构的限制。但对于本就缓存容量有限的Celeron来说,256KB到512KB的提升,绝对是相当有意义的一步。

先前针对新赛扬的文章主要集中于Celeron D 356身上,而352的实力则不为人知,今天台湾网友jeffchen在论坛发表了自己Celeron D 352的测试成绩,我们一起来看看。

关注我们